An open source POWER ISA processor core — derived from the A2O design, updated to current specification, and available for FPGA deployment, ASIC tape-out, or multi-foundry silicon manufacturing.

The Power Instruction Set Architecture is open and royalty-free. IBM's patent coverage, provided through OpenPOWER Foundation membership, means any organization can design and manufacture a POWER-compliant processor without additional IP licensing costs. What has been missing is a production-ready, fully open processor design that implements the current specification.

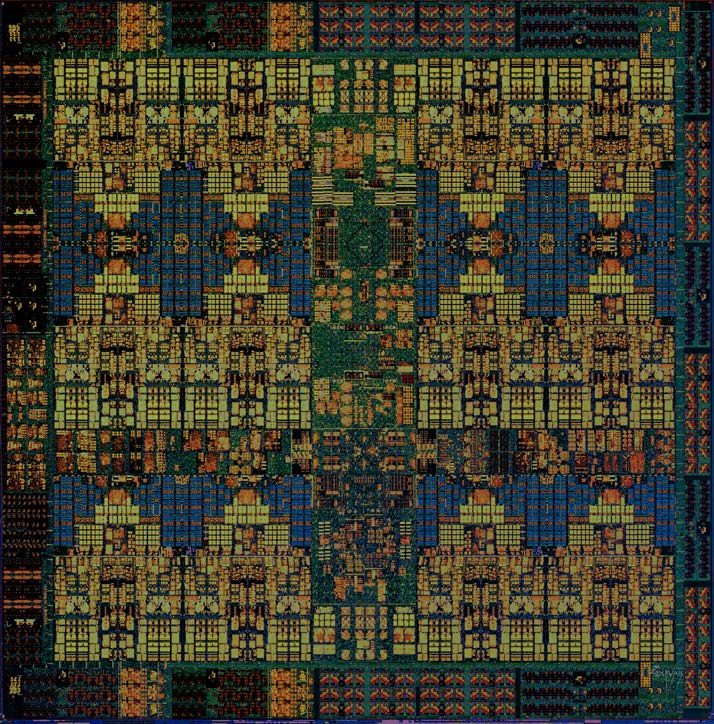

The OpenCore Processor project closes this gap. Starting from IBM's A2O core — a high-performance, out-of-order execution engine released as open source — and collaborating with POWER Commons and LibrePOWER on POWER ISA compliance and physical implementation, this project delivers a processor that consortium members can synthesize in FPGA, tape out at a commercial foundry, or deploy as a verified soft core in custom silicon.

For regulated industries operating IBM POWER infrastructure, this represents the foundational layer of sovereign compute: a processor whose entire design is auditable, whose manufacturing is not controlled by a single company, and whose continued development is governed by a neutral foundation.

IBM POWER10 and POWER11 processors are manufactured exclusively by IBM and IBM's foundry partners, with no disclosed design files, no third-party manufacturing option, and no mechanism for independent verification of the silicon. For national security agencies, critical financial infrastructure, and regulated healthcare systems, this creates three concrete problems:

The Power ISA being open does not solve these problems unless there is also an open, implemented design. The OpenCore project provides that design.

The project builds on proven components rather than starting from scratch:

Complete gap analysis between A2O and POWER ISA, with implementation priority ranking and effort estimates. Month 3.

Synthesizable Verilog/SystemVerilog with all POWER ISA features implemented and verified. Month 18.

Verified bitstream for target FPGA platforms. Boots Linux, passes ISA compliance test suite. Month 12.

Open source ISA compliance test suite, co-simulation harness, and formal verification scripts. Ongoing.

Production-ready GDSII for tape-out at target process node, including timing closure and DRC-clean layout. Month 36.

SoC integration guide, bus interface documentation, and reference memory subsystem for OCP platform integration. Month 24.

This project does not start from zero. The following existing open source efforts are incorporated as collaborators and dependencies:

A2O Core (IBM/GitHub) POWER Commons LibrePOWER skiboot/OPAL Microwatt (reference)

The project steering committee will coordinate with POWER Commons on physical implementation methodology and with LibrePOWER on open EDA toolchain qualification. Microwatt serves as a compliance reference for simpler ISA features.

The OpenCore Processor project operates under the OpenPOWER Foundation's project governance framework:

A fully open processor design is not an academic exercise. For a tier-1 bank operating a POWER estate, it means the ability to commission an independent audit of the silicon executing at the highest privilege level in their infrastructure. For a national government agency, it means processor supply from any qualified foundry — including domestic fabs — without sole-source dependency on a US commercial vendor. For a healthcare system, it means long-term continuity independent of any single company's product lifecycle decisions.

Combined with the OpenFSP, OpenHMC, and OCP Reference Platform projects, the OpenCore processor completes a full open source stack for POWER-class enterprise compute.